User Manual for the Atari ST

Bit-Block Transfer Processor (BLiTTER)

The Atari Corporation Sunnyvale, California 17 June 1987

# Table of Contents

| 1.  | Int   | rodi | ıcti | on .  | • • • | • • • |     |      | • • • | • • | • • | • • | • • | • • | • • | •  | • • | • • | •   | • • | •   | • | 2           |

|-----|-------|------|------|-------|-------|-------|-----|------|-------|-----|-----|-----|-----|-----|-----|----|-----|-----|-----|-----|-----|---|-------------|

| 2.  | Bit   | -B10 | ock  | Tran  | sfe   | rs    |     |      | • • • | • • |     | • • |     | • • | • • | •  |     | • • | •   | • • |     | • | 4           |

| з.  | Fun   | ctic | nal  | Des   | cri   | pti   | on  |      | • • • | ••  | • • | • • | ••  | • • |     | •  | • • | • • | •   | • • |     | • | 6           |

| 4.  | Pro   | gran | nmir | ng Mo | del   |       |     |      |       |     |     |     | ••  |     |     | •  | • • |     |     | •   |     | • | 8<br>8<br>9 |

|     |       |      |      | ter M |       |       |     |      |       |     |     |     |     |     |     |    |     |     |     |     |     |   | 8           |

| -   |       |      | -    | lock  |       |       |     |      |       |     |     |     |     |     |     |    |     |     |     |     |     |   |             |

| 4   | .3.   | Bi   | t-BJ | lock  | Ali   | gnm   | ent | ts . |       | • • | • • | • • |     |     | • • |    | • • | • • |     | •   | • • | • | 11          |

| 4   | .4.   | Lo   | gic  | Oper  | ati   | ons   |     |      |       |     |     |     |     |     |     | •  |     |     |     | •   |     | • | 12          |

| 4   | .5.   | Ha   | ĺfto | one C | ber   | ati   | ons | 3    |       |     |     |     |     |     |     |    |     | • ( |     | •   |     |   | 13          |

| _   | .6.   |      |      | cess  |       |       |     |      |       |     |     |     |     |     |     |    |     |     |     |     |     |   |             |

| App | endi: | x A  |      | Prog  | ran   | min   | g I | Exam | ple   | ∍ . |     | • • | • • |     | • • | •  |     | •   | • • | •   | • • | • | 15          |

| App | endi: | х В  |      | Exte  | nde   | d S   | T I | BIOS | В     | lit | C   | on  | fi  | gu  | ıra | at | ic  | n   | •   | •   | • • |   | 23          |

| aaA | endi  | x C  |      | Refe  | ren   | ces   |     |      |       |     |     |     |     |     |     |    |     | •   |     | •   | • ( |   | 25          |

```

$Header: blitter.me,v 2.2 87/06/17 14:50:06 art Exp $

$Source: /u/art/0_docs/RCS/blitter.me,v $

$Author: art $

SRevision: 2.2 $

$Date: 87/06/17 14:50:06 $

$State: Exp $

$Locker: art $

$Log:

blitter.me, v $

Revision 2.2 87/06/17 14:50:06 art

Added new appendix for extended ST BIOS call.

Revision 2.1 87/06/15 15:10:54 art

Released.

Revision 1.3 87/06/15 14:58:36 art

Changed Bit-Block Transfers section after internal review.

Revision 1.2 87/06/12 02:28:39 art

Cleaned up previous hack.

Revision 1.1 87/06/02 13:58:33 art

Initial revision

```

THE SCOPE OF THIS DOCUMENT is limited to a functional description of the Atari ST BLITTER. This document is not a data sheet for system integration, rather it is a user manual for system programming. For more information, please refer to the texts listed at the end of this document.

### 1. Introduction

The Atari ST Bit-Block Transfer Processor (BLITTER) is a hardware implementation of the bit-block transfer (BitBlt aka blit) algorithm. BitBlt can be simply described as a procedure that moves bit-aligned data from a source location to a destination location through a given logic operation. The BitBlt primitive can be used to perform such operations as:

- o Area seed filling

- o Rotation by recursive subdivision

- o Slice and smear magnification

- o Brush line drawing using Bresenham DDA

- o Text transformations eg bold, italic, outline

- o Text scrolling

- o Window updating

- o Pattern filling

And general memory-to-memory block copying [1].

The heart of BitBlt was first formally defined by Newman and Sproull in their description of the function RasterOp [2]. As defined, RasterOp performed its block transfers on a bit-by-bit basis and was limited to a small subset of possible source and destination Boolean combinations. Enhancements to RasterOp such as processing bits in parallel or introducing a halftone pattern into the transfer were literally left as exercises for the reader.

In an effort to improve the functionality and performance of the original algorithm, the prescribed enhancements were incorporated into the definition of RasterOp and implemented in hardware as the RasterOp Chip [3]. However the RasterOp Chip lacked the two-dimensionality of the original function and suffered from a performance bottleneck caused by the loading and reloading of source, destination, and halftone data (ie it could not DMA).

While efforts were being made to improve the performance of RasterOp, the formal definition of RasterOp was further refined and became the basis of the BitBlt copyLoop primitive in the Smalltalk-80 graphics kernel [4]. Because of its comprehensive interface definition, the BitBlt

primitive was inefficient and required special-case optimizations that violated its general-purpose nature. Clearly a hardware solution was necessary to increase the performance of the BitBlt copyLoop without sacrificing its functionality.

The Atari ST BLITTER is a hardware solution to the performance problems of BitBlt. The BLITTER is a DMA device that implements the full BitBlt copyLoop definition with the addition of a few minor extensions. Single word or multiword increments and decrements are provided for transfers to destinations in Atari ST video display memory. A center mask, which would otherwise be a constant all ones, is also provided for an additional level of texture. The remainder of this document is irectly based on the original functional description of the Atari ST BLITTER.

#### 2. Bit-Block Transfers

As previously stated, a bit-block transfer can be described as a procedure that moves bit-aligned data from a source location to a destination location through a given logic operation. There are sixteen logic combination rules associated with the merging of source and destination data. Note that this set contains all possible combinations between source and destination. The following table contains the valid BitBlt combination rules:

#### LOGIC OPERATIONS

| (~s&~d) (~s&d) (s&~d) (s&<br>MSB LS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | OP               | COMBINATION RULE                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       0       0       0       0         0       0       0       1       0         0       0       1       0       0         0       1       0       0       0       1         0       1       1       0       0       1       1       1       1         0       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1 <td< td=""><td>0123456789ABCDEF</td><td>all zeros source AND destination source NOT source AND destination destination source XOR destination source OR destination NOT source AND NOT destination NOT source XOR destination NOT destination NOT destination source OR NOT destination NOT source NOT source NOT source NOT source OR destination NOT source NOT source OR destination NOT source OR NOT destination NOT source OR NOT destination all ones</td></td<> | 0123456789ABCDEF | all zeros source AND destination source NOT source AND destination destination source XOR destination source OR destination NOT source AND NOT destination NOT source XOR destination NOT destination NOT destination source OR NOT destination NOT source NOT source NOT source NOT source OR destination NOT source NOT source OR destination NOT source OR NOT destination NOT source OR NOT destination all ones |

Adjustments to block extents and several other transfer parameters are determined prior to the invocation of the actual block transfer. These adjustments and parameters include clipping, skew, end masks, and overlap.

Clipping. The source and destination block extents are adjusted to conform with a specified clipping rectangle. Since both source and destination blocks are of equal dimension, the destination block extent is clipped to the extent of the source block (or vice versa). Note that the block transfer need not be performed if the resultant extent is zero.

Skew. The source-to-destination horizontal bit skew is calculated.

End Masks. The left and right partial word masks are determined. The masks are merged if the destination is one word in width.

Overlap. The block locations are checked for possible overlap in order to avoid the destruction of source data before it is transferred.

In non-overlapping transfers the source block scanning direction is inconsequential and can by default be from upper left to lower right. In overlapping transfers the source scanning direction is also from upper left to lower right if the source-to-destination transfer direction is up and/or to the left (ie source address is greater than or equal to destination address). However, if the overlapping source-to-destination transfer direction is down and/or to the right (ie source address is less than destination address), then the source data is scanned from lower right to upper left.

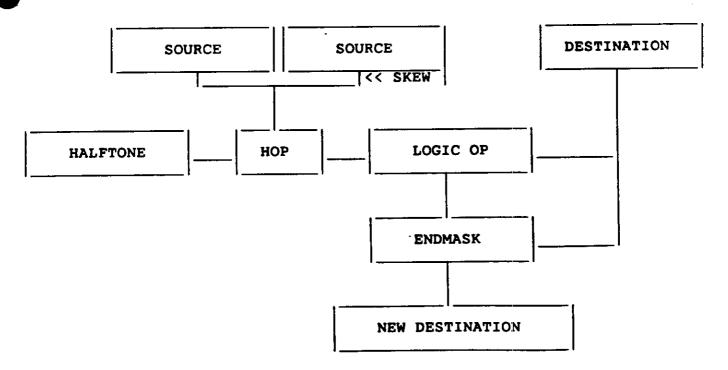

After the transfer parameters are determined the bitblock transfer operation can be invoked, transferring source to destination through the logic operation (HALFTONE and HOP will be described in the next section):

# BIT-BLOCK TRANSFER

The Atari Corporation

# 3. Functional Description

Please refer to the bit-block transfer diagram in the previous section. To understand how the components of a block transfer work, let's look at the simplest possible transfer. Take the case where we wish to fill a block of memory with either all zeros or all ones (OP = 0 or OP = F). In this case only the LOGIC OP block, which generates the ones or zeros, and the ENDMASK block are in the data path. If the end mask contains all ones, the BLITTER will simply write one word after the other to the destination address without ever reading the destination.

As the writes take place the destination address will be adjusted according to the values in the DESTINATION X INCREMENT, DESTINATION Y INCREMENT, X COUNT, and Y COUNT registers. These registers define the size and shape of the block to be transferred. The X and Y COUNT registers define the size of the block. The X COUNT register specifies the number of word-size writes required to update one line of the destination. The Y COUNT register specifies the number of these lines in the block. The DESTINATION X INCREMENT register is a signed (2's complement) 16-bit quantity which is added to the destination address to calculate the address of the next destination word of the line. On the last write of the line the DESTINATION Y INCREMENT is added to calculate the address of the first word of the next line.

The end mask determines which bits of the destination word will be updated. Bits of the destination which correspond to ones in the end mask will be updated. Bits of the destination which correspond to zeros in the end mask will remain unchanged. Note that if any bits of the destination are to be left unchanged, a read-modify-write is required. In order to improve performance a read will only be performed if it is required. There are three ENDMASK registers numbered 1 through 3. ENDMASK 1 is used only for the first write of the line. ENDMASK 3 is used only for the last write of the line. ENDMASK 2 is used for all other writes.

Now let's consider a more complicated case, suppose we want to XOR a destination block with a 16x16 halftone pattern. First we load the HALFTONE RAM with the halftone pattern. Select halftone only using the HOP register and select source XOR destination using the OP register. The LINE NUMBER register is used to specify which of the 16 words of HALFTONE RAM is used for the current line. This register will be incremented or decremented at the end of each line according to the sign of the DESTINATION Y INCREMENT register. Set the DESTINATION X and Y INCREMENT and X and Y COUNT registers to the appropriate values and start the transfer. This same procedure can be followed to do the

combination using any logic operation by simply changing the value in the OP register. Similarly the combination can be performed using a source block instead of the HALFTONE RAM or using the logical AND of a source block and the HALFTONE RAM by changing the value of the HOP register. A source block is the same size as the destination block but may have different increments and address defined by the SOURCE X and Y INCREMENT and SOURCE ADDRESS registers.

Finally, let's look at the case when the source destination blocks are not bit-aligned. In this case we may need to read the first two source words into the 32-bit source buffer and use the 16 bits that line up with the appropriate bits of the destination, as specified by the SKEW register. When the next source word is read, the lower 16 bits of the source buffer is transferred to the upper 16 bits and the lower is replaced by the new data. This process is reversed when the source is being read from the right to the left (SOURCE X INCREMENT negative). Since there are cases when it may be necessary for an extra source read to be performed at the beginning of each line to "prime" the source buffer and cases when it may not be necessary due to the choice of end mask, a bit has been provided which forces the extra read. The FXSR (aka pre-fetch) bit in the SKEW register indicates, when set, that an extra read should be performed at the beginning of each source read should be performed at the beginning of each line to "prime" the source buffer. Similarly the NFSR (aka post-flush) bit, when set, will prevent the last source read This read may not be necessary with certain of the line. combinations of end masks and skews. If the read is suppressed, the lower to upper half buffer transfer still occurs. Also in this case, a read-modify-write cycle is performed on the destination for the last write of each line regardless of the value of the corresponding ENDMASK register.

-48 Are

### 4. Programming Model

The BLITTER contains a set of registers that specify bit-block addresses, bit-block alignments, logic and halftone operations, and bus accesses. The register set-up time remains practically constant and is large relative to small block transfers, whereas large bit-blocks are dominated by the execution time of the transfer itself.

# 4.1. Register Map

The following is a map of the BLiTTER programmable registers (note that all unused bits read back as zeros):

### REGISTER MAP

| FF | 8A00 | 00000000   000000000 | HALFTONE RAM            |

|----|------|----------------------|-------------------------|

| FF | 8A02 | 00000000 00000000    |                         |

| FF | 8A04 | 00000000 00000000    |                         |

|    |      |                      |                         |

| FF | 8A1E | 00000000 00000000    |                         |

| FF | 8A20 | 00000000 0000000-    | SOURCE X INCREMENT      |

| FF | 8A22 | 0000000 000000-      | SOURCE Y INCREMENT      |

| FF | 8A24 | 00000000             | SOURCE ADDRESS          |

| FF | 8A26 | 0000000 0000007      |                         |

| FF | 8A28 | 00000000   00000000  | ENDMASK 1               |

| FF | 8A2A | 00000000 00000000    | ENDMASK 2               |

| FF | 8A2C | 00000000 00000000    | ENDMASK 3               |

| FF | 8A2E | 00000000   0000000-  | DESTINATION X INCREMENT |

| FF | 8A30 | 00000000   0000000-  | DESTINATION Y INCREMENT |

| FF | 8A32 | 00000000             | DESTINATION ADDRESS     |

| FF | 8A34 | 00000000   0000000-  |                         |

| FF | 8A36 | 00000000   00000000  | X COUNT                 |

| FF | 8A38 | 00000000   00000000  | Y COUNT                 |

|    |      |                      |                         |

| FF | 8A3A | 00                   | НОР                     |

| FF | 8A3B | 0000                 | OP                      |

|    |      |                      |                         |

| FF | 8A3C | 000-0000             |                         |

|    |      | ·                    | LINE NUMBER             |

|    |      |                      | SMUDGE                  |

|    |      |                      | HOG                     |

|    |      |                      | BUSY                    |

|    |      |                      |                         |

| FF | 8A3D | oooooo               | A cross s               |

|    |      |                      | _ SKEW                  |

|    |      |                      | NFSR                    |

|    |      |                      | FXSR                    |

|    |      |                      |                         |

### 4.2. Bit-Block Addresses

This subsection describes registers that specify bitblock origins, address increments, and extents.

#### SOURCE ADDRESS

This 23-bit register contains the current address of the source field (only word addresses may be specified). It may be accessed using either word or longword instructions. The value read back is always the address of the next word to be used in a source operation. It will be updated by the amounts specified in the SOURCE X INCREMENT and the SOURCE Y INCREMENT registers as the transfer progresses.

# SOURCE X INCREMENT

This is a signed 15-bit register, the least significant bit is ignored, specifying the offset in bytes to the address of the next source word in the current line. This value will be sign-extended and added to the SOURCE ADDRESS register at the end of a source word fetch, whenever the X COUNT register does not contain a value of one. If the X COUNT register is loaded with a value of one this register is not used. Byte instructions can not be used to read or write this register.

# SOURCE Y INCREMENT

This is a signed 15-bit register, the least significant bit is ignored, specifying the offset in bytes to the address of the first source word in the next line. This value will be sign-extended and added to the SOURCE ADDRESS register at the end of the last source word fetch of each line (when the X COUNT register contains a value of one). If the X COUNT register is loaded with a value of one this register is used exclusively. Byte instructions can not be used to read or write this register.

### DESTINATION ADDRESS

This 23-bit register contains the current address of the destination field (only word addresses may be specified). It may be accessed using either word or long-word instructions. The value read back is always the address of the next word to be modified in the destination field. It will be updated by the amounts specified in the DESTINATION X INCREMENT and the DESTINATION Y INCREMENT registers as the transfer progresses.

# DESTINATION X INCREMENT

This is a signed 15-bit register, the least significant bit is ignored, specifying the offset in bytes to the address of the next destination word in the current

line. This value will be sign-extended and added to the DESTINATION ADDRESS register at the end of a destination word write, whenever the X COUNT register does not contain a value of one. If the X COUNT register is loaded with a value of one this register is not used. Byte instructions can not be used to read or write this register.

### DESTINATION Y INCREMENT

This is a signed 15-bit register, the least significant bit is ignored, specifying the offset in bytes to the address of the first destination word in the next line. This value will be sign-extended and added to the DESTINATION ADDRESS register at the end of the last destination word write of each line (when the X COUNT register contains a value of one). If the X COUNT register is loaded with a value of one this register is used exclusively. Byte instructions can not be used to read or write this register.

#### X COUNT

This 16-bit register specifies the number of words contained in one destination line. The minimum number is one and the maximum is 65536 designated by zero. Byte instructions can not be used to read or write this register. Reading this register returns the number of destination words yet to be written in the current line, NOT necessarily the value initially written to the register. Each time a destination word is written the value will be decremented until it reaches zero, at which time it will be returned to its initial value.

### Y COUNT

This 16-bit register specifies the number of lines in the destination field. The minimum number is one and the maximum is 65536 designated by zero. Byte instructions can not be used to read or write this register. Reading this register returns the number of destination lines yet to be written, NOT necessarily the value initially written to the register. Each time a destination line is completed the value will be decremented until it reaches zero, at which time the transfer is complete.

### 4.3. Bit-Block Alignments

This subsection describes registers that specify bitblock end masks, source-to-destination skew, and source data fetching.

ENDMASK 1, 2, 3

These 16-bit registers are used to mask destination writes. Bits of the destination word which correspond to ones in the current ENDMASK register will be modified. Bits of the destination word which correspond to zeros in the current ENDMASK register will remain unchanged. The current ENDMASK register is determined by position in the line. ENDMASK 1 is used only for the first write of a line. ENDMASK 3 is used only for the last write of a line. ENDMASK 2 is used in all other cases. In the case of a one word line ENDMASK 1 is used. Byte instructions can not be used to read or write these registers.

SKEW

The least significant four bits of the byte-wide register at FF 8A3D specify the source skew. This is the amount the data in the source data latch is shifted right before being combined with the halftone mask and destination data.

**FXSR**

FXSR stands for Force eXtra Source Read. When this bit is set one extra source read is performed at the start of each line to initialize the remainder portion source data latch.

NFSR

NFSR stands for No Final Source Read. When this bit is set the last source read of each line is not performed. Note that use of this and/or the FXSR bit the requires an adjustment to the SOURCE Y INCREMENT and SOURCE ADDRESS registers.

# 4.4. Logic Operations

This subsection describes registers that specify the logic combinations of source and destination bit-block data.

OP

The least significant four bits of the byte-wide register at FF 8A3B specify the source/destination combination rule according to the following table:

### LOGIC OPERATIONS

| OP     | COMBINATION RULE               |

|--------|--------------------------------|

| 0      | all zeros                      |

| 1      | source AND destination         |

| 2      | source AND NOT destination     |

| 2<br>3 | source                         |

| 4      | NOT source AND destination     |

| 5      | destination                    |

| 6      | source XOR destination         |

| 7      | source OR destination          |

| 8      | NOT source AND NOT destination |

| 9      | NOT source XOR destination     |

| À      | NOT destination                |

| B      | source OR NOT destination      |

| Č      | NOT source                     |

|        |                                |

| D      | NOT source OR destination      |

| E      | NOT source OR NOT destination  |

| F      | all ones                       |

# 4.5. Halftone Operations

This subsection describes registers that specify the halftone pattern memory, halftone word index, and combinations of source and halftone data.

#### HALFTONE RAM

This RAM holds a 16x16 halftone pattern mask. Each word is valid for one line of the destination field and is repeated every 16 lines. The current word is pointed to by the value in the LINE NUMBER register. These registers may be read, but can not be accessed using byte-wide instructions.

### LINE NUMBER

The least significant four bits of the byte-wide register at FF 8A3C specify the current halftone mask. The current value times two plus FF8A00 gives the address of the current halftone mask. This value is incremented or decremented at the end of each line and will wrap through zero. The sign of the DESTINATION Y INCREMENT determines if the line number is incremented or decremented (increment if positive, decrement if negative).

#### **SMUDGE**

The SMUDGE bit, when set, causes the least significant four bits of the skewed source data to be used as the address of the current halftone pattern. Note that the halftone operation is still valid when SMUDGE is set.

### HOP

The least significant two bits of the byte-wide register at FF 8A3A specify the source/halftone combination rule according to the following table:

#### HALFTONE OPERATIONS

| НОР              | COMBINATION RULE                             |

|------------------|----------------------------------------------|

| 0<br>1<br>2<br>3 | all ones halftone source source AND halftone |

- AMERICAN

### 4.6. Bus Accesses

This subsection describes registers that specify bus access control and BLiTTER start/status.

HOG

The HOG bit, when cleared, causes the processor and the BLITTER to share the bus equally. In this mode each will get 64 bus cycles while the other is halted. When set, the bit will cause the processor to be halted until the transfer is complete. In either case the BLITTER will yield to other DMA devices. Bus arbitration may allow the processor to execute one or more instructions even in hog mode. Therefore, don't assume that the instruction following the one which sets the BUSY bit will be executed only after the transfer is complete. The BUSY bit may be polled to achieve this kind of synchronization.

**BUSY**

The BUSY bit is set after all the other registers have been initialized to begin the transfer operation. It will remain set until the transfer is complete. The interrupt line is a duplicate of this bit. See the Programming Example for more details on how to use the BUSY bit.

# Appendix A -- Programming Example

In order to maintain software compatibility with new or upgraded Atari STs equipped with the BLiTTER, software developers need only follow guidelines set forth by the VDI and "LINE A" documents. Revised TOS ROMs will work in concert with the BLiTTER, enhancing the performance of many VDI and "LINE A" operations. This occurs in a manner transparent to an executing program. Thus no special actions need be taken to utilize the performance advantages of the BLiTTER.

As a rule of thumb, never make a VDI or "LINE A" call from within an interrupt context since unpredictable and potentially catastrophic results will occur should one BLiTTER operation interrupt another BLiTTER operation.

The following program has not been optimized and is presented here for exemplary purposes only.

BLiTTER equ \$FF8A00

#### \* BLITTER REGISTER OFFSETS

| Halftone | egu | 0  |

|----------|-----|----|

| Src Xinc | equ | 32 |

| Src Yinc | equ | 34 |

| Src Addr | equ | 36 |

| Endmaskl | equ | 40 |

| Endmask2 | equ | 42 |

| Endmask3 | equ | 44 |

| Dst Xinc | equ | 46 |

| Dst Yinc | equ | 48 |

| Dst Addr | equ | 50 |

| X Count  | equ | 54 |

| Y Count  | equ | 56 |

| HŌP      | equ | 58 |

| OP       | equ | 59 |

| Line Num | equ | 60 |

| Skew_    | equ | 61 |

|          |     |    |

<sup>\* (</sup>c) 1987 Atari Corporation \* All Rights Reserved.

<sup>\*</sup> BLITTER BASE ADDRESS

```

* BLITTER REGISTER FLAGS

fHOP Source

equ

fHOP Halftone

0

equ

fSkewFXSR

equ

6

fSkewNFSR

equ

7

fLineBusy

equ

6

equ

fLineHog

5

equ

fLineSmudge

* BLITTER REGISTER MASKS

mHOP_Source

mHOP_Halftone

$02

equ

$01

equ

$80

mSkewFXSR

equ

mSkewNFSR

$40

equ

$80

egu

mLineBusy

$40

equ

mLineHog

$20

mLineSmudge

equ

data

EnDmask

* These tables are referenced by PC relative instructions.

* the labels on these tables must remain within 128 bytes of the

* referencing instructions forever. Amen.

* 0: Destination 1: Source <<< Invert right end mask data >>>

lf endmask:

$FFFF

dc.w

rt endmask:

$7FFF

dc.w

$3FFF

dc.w

$1FFF

dc.w

dc.w

SOFFF

dc.w

$07FF

$03FF

dc.w

dc.w

$01FF

$00FF

dc.w

dc.w

$007F

dc.w

$003F

dc.w

$001F

$000F

dc.w

dc.w

$0007

$0003

dc.w

$0001

dc.w

```

\$0000

dc.w

```

TiTLE:

BLIT IT

Transfer a rectangular block of pixels located at an

* Purpose:

arbitrary X,Y position in the source memory form to

another arbitrary X,Y position in the destination memory

form using replace mode (boolean operator 3).

The source and destination rectangles should not overlap.

* in:

*

pointer to 34 byte input parameter block

a4

This routine must be executed in supervisor mode as access

* NoTe:

is made to hardware registers in the protected region of the

\star

memory map.

*

Input parameter

B 1 0 c K

offSeTs

O ; Base address of source memory form

SRC FORM

equ

. 1

SRC NXWD

equ

4 ; Offset between words in source plane

. W

SRC NXLN

6; Source form width

.w

equ

SRC_NXPL

SRC_XMIN

8 ; Offset between source planes

.w

egu

10 ; Source blit rectangle minimum X

.w

equ

12 ; Source blit rectangle minimum Y

. W

SRC YMIN

egu

14; Base address of destination memory form

.1

DST FORM

equ

18 ; Offset between words in destination plane .w

DST NXWD

equ

20; Destination form width

STNXLN

eau

. W

DST NXPL

22 : Offset between destination planes

. W

equ

DST XMIN

24 ; Destination blit rectangle minimum X

. W

equ

DST YMIN

26; Destination blit rectangle minimum Y

. W

egu

egu

28; Width of blit rectangle

. W

WIDTH

HEIGHT

equ

30 ; Height of blit rectangle

.W

PLANES

equ

32; Number of planes to blit

.W

BLIT IT:

; a5-> BLiTTER register block

BLITTER, a5

lea

Calculate Xmax coordinates from Xmin coordinates and width

move.w WIDTH(a4),d6

: d6<- width-1

subq.w

#1,d6

: d0<- src Xmin

SRC XMIN(a4),d0

move.w

d0, d1

move.w

; dl<- src Xmax = src Xmin + width-l

add.w

d6, d1

DST XMIN(a4),d2

; d2<- dst Xmin

move.w

d2, \overline{d}3

move.w

: d3<- dst Xmax = dst Xmin + width-l

add.w

d6,d3

```

The Atari Corporation

```

Endmasks are derived from source Xmin mod 16 and source Xmax mod 16

; d6<- mod 16 mask

moveq.1 #$0F,d6

; d4<- DST XMIN

d2,d4

move.w

; d4<- DST XMIN mod 16

a6, a4

and.w

; d4<- offset into left end mask tbl

add.w

d4,d4

move.w lf_endmask(pc,d4.w),d4 ; d4<- left endmask

; d5<- DST_XMAX

move.w

d3,d5

; d5<- DST XMAX mod 16

d6,d5

and.w

; d5<- offset into right end mask tbl

add.w

d5,d5

rt endmask(pc,d5.w),d5; d5<- inverted right end mask

move.w

; d5<- right end mask

d5

not.w

Skew value is (destination Xmin mod 16 - source Xmin mod 16)

Three discriminators are used to determine the

&& Ox000F.

states of FXSR and NFSR flags:

0: Source Xmin mod 16 =< Destination Xmin mod 16

*

bit 0

1: Source Xmin mod 16 > Destination Xmin mod 16

*

*

O: SrcXmax/16-SrcXmin/16 <> DstXmax/16-DstXmin/16

×

bit 1

Destination span

Source span

1: SrcXmax/16-SrcXmin/16 == DstXmax/16-DstXmin/16

O: multiple word Destination span

bit 2

1: single word Destination span

These flags form an offset into a skew flag table yielding

correct FXSR and NFSR flag states for the given source and

destination alignments

; d7<- Dst Xmin

move.w

d2,d7

; d7<- Dst Xmin mod16

and.w

d6, d7

; d6<- Src Xmin mod16

and.w

d0,d6

; d7<- Dst Xmin mod16-Src Xmin mod16

sub.w

d6,d7

; if Sx&F > Dx&F then cy:1 else cy:0

; d6<- initial skew flag table index

clr.w

d6

; d6[bit0]<- intraword alignment flag

addx.w

d6,d6

; dO<- word offset to src Xmin

lsr.w

#4,d0

; dl<- word offset to src Xmax

#4,d1

lsr.w

; d1<- Src span - 1

sub.w

d0.d1

; d2<- word offset to dst Xmin

#4,d2

lsr.w

; d3<- word offset to dst Xmax

lsr.w

#4,d3

; d3<- Dst span - 1

sub.w

d2,d3

; 2nd discriminator is one word dst

set endmasks

bne

```

ز. کائیته زر

-

```

* When destination spans a single word, both end masks are merged

* into Endmask1. The other end masks will be ignored by the BLiTTER

; d4<- single word end mask

and.w

d5,d4

; d6[bit2]:1 => single word dst

addq.w #4,d6

set endmasks:

; left end mask

move.w d4,Endmask1(a5)

move.w #$FFFF, Endmask2(a5); center end mask

move.w d5, Endmask3(a5) ; right end mask

; the last discriminator is the

d1,d3

CMD.W

; equality of src and dst spans

set_count

bne

; d6[bit1]:1 => equal spans

addq.w #2,d6

set_count:

move.w d3,d4

; d4<- number of words in dst line

addq.w #1,d4

; set value in BLiTTER

move.w d4,X Count(a5)

* Calculate Source starting address:

×

Source Form address

(Source Ymin * Source Form Width) +

* ((Source Xmin/16) * Source Xinc)

move.u SRC_YMIN(a4),a0 ; a0-> start of Src form move.w SRC_YMIN(a4),d4 ; d4<- offset in lines to Src Ymin move.w SRC_NXLN(a4),d5 ; d5<- length of Src form line d5,d4 ; d4<- books add 1 d4<- books and 24 d4

; a0->(\bar{0}, Ymin)

add.1

d4,a0

move.w SRC NXWD(a4),d4 ; d4<- offset between consecutive

words in Src plane

move.w d4, Src_Xinc(a5)

; dO<- offset to word containing Xmin

d4, d0

mulu

; a0-> 1st src word (Xmin, Ymin)

add.l

d0, a0

* Src_Yinc is the offset in bytes from the last word of one Source

* line to the first word of the next Source line

; dl<- width of src line in bytes

d4, d1

mulu

; d5<- value added to pointer at end

d1,d5

sub.w

of line to reach start of next

move.w d5,Src Yinc(a5)

* Calculate Destination starting address

move.1 DST_FORM(a4),a1 ; a1-> start of dst form move.w DST_YMIN(a4),d4 ; d4<- offset in lines to dst Ymin move.w DST_NXLN(a4),d5 ; d5<- width of dst form

; al-> start of dst form

```

```

; d4<- byte offset to (0, Ymin)

d5, d4

mulu

; al-> dst (0, Ymin)

add.l

d4,al

; d4<- offset between consecutive

DST NXWD(a4),d4

move.w

words in dst plane

move.w d4, Dst_Xinc(a5)

; d2<- DST NXWD * (DST XMIN/16)

mulu

d4, d2

; al-> 1st dst word (Xmin, Ymin)

add.l

d2,a1

* Calculate Destination Yinc

; d3<- width of dst line - DST NXWD

d4,d3

mulu

; d5<- value added to dst pointer at

sub.w d3,d5

move.w d5,Dst_Yinc(a5)

end of line to reach next line

* The low nibble of the difference in Source and Destination alignment

* is the skew value. Use the skew flag index to reference FXSR and NFSR

* states in skew flag table.

; d7<- isolated skew count

and.b

#$OF, d7

skew_flags(pc,d6.w),d7; d7<- necessary flags and skew

or.b

; load Skew register

move.b d7, Skew(a5)

move.b #mHOP Source, HOP(a5); set HOP to source only move.b #3,OP(a5); set OP to "replace" modern move.b

; set OP to "replace" mode

; fast ref to Line Num register

Line Num(a5),a2

lea

; fast ref to LineBusy flag

move.b #fLineBusy,d2

; d7 <- plane counter

move.w PLANES(a4),d7

begin

bra

```

```

F1AgS

s E t T i N g

0 f

SKEW

BITBLT DIRECTION: LEFT -> RIGHT

QUALIFIERS

ACTIONS

equal Sx&F>

spans Dx&F FXSR NFSR

*

0

0

......

0

1

1

..dadddddddddddddddddd..

1

0

0

...ddddddddddddddddddddddddd.

1

1

1

..dddddddddddddddddddd..

skew_flags:

; Source span < Destination span

dc.b

mSkewNFSR

; Source span > Destination span

mSkewFXSR

dc.b

; Spans equal Shift Source right

dc.b

mSkewNFSR+mSkewFXSR; Spans equal Shift Source left

dc.b

* When Destination span is but a single word ...

; Implies a Source span of no words

dc.b

; Source span of two words

dc.b

mSkewFXSR

; Skew flags aren't set if Source and

dc.b

0

; Destination spans are both one word

dc.b

0

```

```

next plane:

```

```

move.l a0, Src_Addr(a5) ; load Source pointer to this plane move.l a1, Dst_Addr(a5) ; load Destination ptr to this plane move.w HEIGHT(a4), Y_Count(a5) ; load the line count move.b #mLineBusy, (a2) ; <<< start the BLiTTER >>> add.w SRC_NXPL(a4), a0 ; a0-> start of next src plane add.w DST_NXPL(a4), a1 ; a1-> start of next dst plane

```

\* The BLITTER is usually operated with the HOG flag cleared.

\* In this mode the BLITTER and the ST's cpu share the bus equally,

\* each taking 64 bus cycles while the other is halted. This mode

\* allows interrupts to be fielded by the cpu while an extensive

\* BitBlt is being processed by the BLITTER. There is a drawback in

\* that BitBlts in this shared mode may take twice as long as BitBlts

\* executed in hog mode. Ninety percent of hog mode performance is

\* achieved while retaining robust interrupt handling via a method

\* of prematurely restarting the BLITTER. When control is returned

\* to the cpu by the BLITTER, the cpu immediately resets the BUSY

\* flag, restarting the BLITTER after just 7 bus cycles rather than

\* after the usual 64 cycles. Interrupts pending will be serviced

\* before the restart code regains control. If the BUSY flag is

\* reset when the Y Count is zero, the flag will remain clear

\* indicating BLITTER completion and the BLITTER won't be restarted.

\* (Interrupt service routines may explicitly halt the BLiTTER

\* during execution time critical sections by clearing the BUSY flag.

\* The original BUSY flag state must be restored however, before

\* termination of the interrupt service routine.)

#### restart:

```

bset.b d2,(a2) ; Restart BLiTTER and test the BUSY nop ; flag state. The "nop" is executed bne restart ; prior to the BLiTTER restarting. ; Quit if the BUSY flag was clear.

```

begin: dbra d7, next plane

rts

# Appendix B -- Extended ST BIOS Blit Configuration

0x40 Blitmode - Get/Set Blit Configuration

Synopsis:

WORD Blitmode(flag)

WORD flag;

Extended ST BIOS (trap #14) function number 0x40 (64 decimal) gets and sets the blit configuration. If FLAG is -1 (0xffff), then no set operation is performed, and the current blit configuration is returned. If FLAG is not -1, then the blit configuration is set as follows:

bit 0: 0: set blit mode to soft (use software)

1: set blit mode to hard (use BLiTTER)

bits 1..14: undefined, reserved

bit 15: must be zero

The previous blit configuration is returned in the low word of DO. The fields are:

bit 0: 0: blits are being done in software

1: blits are being done in hardware

bit 1: 0: no BLiTTER is available

1: a BLiTTER is installed in the system

bits 2..14: undefined, reserved, may be zero or one

on return.

bit 15: always returned as zero

If an attempt is made to set the blit mode to "hard" on a system that does not contain a BLITTER, the mode is forced to "soft".

The reserved fields are for future blit capabilities and other graphics chips. They should be treated as "don't care" fields and should be maintained (intact) because they will acquire meaning in the future.

This call works on all ROM versions of the operating system.

```

EXAMPLE CALL USING C

#define Blitmode(a) xbios(64,a)

/* get current mode */

/* turn on BLiTTER */

/* ... do some processing */

/* restore blit state */

curmode = Blitmode(-1);

Blitmode(curmode | 1);

do stuff();

Blitmode(curmode);

EXAMPLE CALL USING 68000 ASSEMBLY

; DO = Blitmode(-1)

move.w \#-1,-(sp)

move.w #$40,-(sp)

trap

#14

addq

#4,sp

; save old blit state

; make sure it's on

; Blitmode(D0)

move.w d0,-(sp)

#1,d0

Or.w

move.w d0,-(sp)

move.w #$40,-(sp)

#14

trap

;

pbbs

#4,sp

;

*

... do some processing

move.w #$40,-(sp)

; restore old blit mode

from stacked old-state

trap

#14

addq

#4, sp

```

- eg. 35-

### Appendix C -- References

- [1] Rob Pike, Leo Guibas, and Dan Ingalls, 'SIGGRAPH'84 Course Notes: Bitmap Graphics', AT&T Bell Laboratories 1984.

- [2] William Newman and Robert Sproull, 'Principles of Interactive Computer Graphics', McGraw-Hill 1979, Chapter 18.

- [3] John Atwood, '16160 RasterOp Chip Data Sheet', Silicon Compilers 1984. See also 'VL16160 RasterOp Graphics/Booleum Operation ALU', VLSI Technology 1986.

- [4] Adele Goldberg and David Robson, 'Smalltalk-80: The Language and its Implementation', Addison-Wesley 1983, Chapter 18.